# Comparison and simulation of a highly linear LNA using 45 nm CMOS process

#### Reza Khoshnood

Electrical Engineering Department, Islamic Azad University, Bandar Abbas Branch.Khoshnood\_r2010@yahoo.com

### Abbas Yarshenas

Electrical Engineering Department, Islamic Azad University, Bandar Abbas Branch.abbasyarsyars@gmail.com

## Farshad Ghaydi

Electrical Engineering Department, Islamic Azad University, Bandar Abbas Branch.Farshad.ghaydi@gmail.com

#### **Abstract:**

This paper focuses on the design of low-power and low-noise (LNA) amplifier functions. Various LNA topologies operating with power consumption under milliwatts at a frequency of 2.4 GHz have been implemented in a 40 nm CMOS commercial process . LNA1 (Common Source LNA Cascad) has an efficiency of 12.22 dB4 noise coefficient (NF) of 4.35 dB4 and third-order input interception point (IIP3) of -12.68 dB at 995.6 µW while proposed LNA2 has been improved. Linearity has increments of 5.68 dB 6 5.13 dB NF 6 and 0.12-dBm IIP3 Is. The difference between both the final designs, which involve linearity and gain increase, comes from the location of gate inductance () in the Nash  $chipL_a$ . The proposed LNA3 with a single chip has an increase in voltage of 11.1 dB, NF 4.27 dB and IIP3 -0.82 dB. In addition,  $L_q$  the proposed LNA4 with an off-chip chip has an increase in voltage of 10.31 dB, NF 3.68 dB and IIP3  $0.89L_g$  dB at 989.6  $\mu$ W in post-layout simulations. By comparison LNAs, the proposed LNA4 with an off-chip chip has the best $L_a$  merit index (FOM). The goal is to achieve improved linear digits at power below milliwatts. The purpose of this paper is to compare the simulation and comparison between the simulation LNA4 with a 40 nm CMOS technology and a 45 nm CMOS technology. The results of the simulation comparison are included in section 4 of the paper. Although the technology used occupies a slightly larger structure, they still have very close

**Keywords:** Low power, Improved linearity, Low noise, CMOS, IMD, Linearization, High frequency circuit

#### 1. Introduction

In recent years, wireless technology has become more vital due to the rapid development of health applications, the Internet of Things (IoT) and Bluetooth Low Energy (BLE) applications. For example, using Bluetooth low-energy technology, instant body signals can be monitored through portable and wireless devices. Body temperature and heart rate sensors are also good examples of biomedical applications [1]. These medical devices such as wireless transmitters and implantable antennas should be small and should operate at very low power. Therefore, biomedical wireless transceivers have been significantly improved due to extensive research on transceiver topologies and design of RF circuits using standard CMOS technology.[2]

A low-noise amplifier (LNA) is the first stage of receivers that amplifies filtered radio frequency (RF) signal with as much noise and distortion as possible. A superheterodyne receiver consists of 5 main blocks: an antenna, an RF filter, a low-noise a mixer and a voltage-controlled amplifier, oscillator. The filtered RF signal received from the antenna is mixed with a local oscillator in the RF receiver chain and pre-converted by the LNA Strengthening. After demodulation, the signal is converted down by analog to digital converter, digitized. LNAs, typically the first and one of the most important stages of the receiver, have a large impact on the overall performance of the receiver. In addition, voltage gain and linearity are important performance criteria for LNAs. LNA must have a high voltage for noise suppression of the next steps [4]. However, power consumption limits these performance metrics. Therefore, the main goal is to minimize the balance between power consumption and high performance.Low power performance is a design problem for voltage and noise increases due to low current levels. Also, linearity, which is characterized by the third-order input interception point (IIP3), corresponds to noise factor and voltage gain [5]. Therefore, linear improvement techniques should be applied to develop linear and low-power LNA designs. In this paper, four low-power LNA that are at a frequency of 2.4 GHz Working with submilliwatt power consumption (below 1 mW), they are implemented in a commercial 40-nanometer CMOS technology .

The first scheme, LNA1, has a high voltage gain and low IIP3 digit, while, through linear improvement techniques, the second design, LNA2, offers better IIP3 performance. However, the voltage gain is significantly reduced by the rise of IIP3. The third topology, LNA3, is developed without reducing the performance of IIP3 to increase the voltage gain The difference between the third and last LNA circuit (LNA4) is whether the  ${\rm chip} L_g$  is included or

not. Hence, this paper focuses on the design challenge of achieving high linearity, even though current levels are very low due to the 1mW power consumption limit. This is a The design problem is difficult because many biomedical tools have to work on limited budgets, but they must deliver high performance. In particular, a highly linear response is expected. This paper shows that, taking LNA4 into account, it is possible to use linear improvement techniques and combine them with design approaches that ensure that voltage gain and noise coefficient are the least effective and remain within their specified range, an IIP3 above 0 dBm produced. In short, the contribution of this work lies in providing design solutions for low-power and highperformance receivers, especially in biomedical applications.

This article has the following structure: The designs of proposed LNAs are described in Part 2. Part 3

discusses the simulation results. Finally, conclusions are drawn in Section 4.

## 2. Circuit description

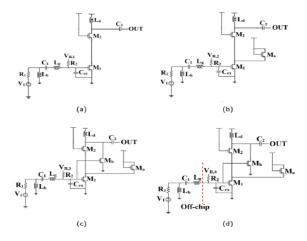

The goal of the four LNA schemes in Figure 1 is to operate with power consumption below milliwatts at 2.4 GHz. LNA1 in Figure 1(a) is the classic LNA cascode. LNA2 in Fig. 1(b) is designed to improve the performance  $M_a$  of IIP3 by adding as an IMD sine. In LNA3, shown in Figure  $1M_b(c)$ , it is added to increase the voltage without reducing the form of IIP3. Also, LNA4 performs the same function as LNA3. It is included  $L_g$  as an on-chip component in LNA3 while it remains off-chip in LNA4, such as Figure 1(d). The bias conditions of all LNAs vary slightly, however they all have an overall power consumption of less than 1 mW. Hence, each LNA is optimized for noise coefficient, voltage gain, and linear performance metrics by observing this limit.

Figure 1-Schematic a) LNA1 b) LNA2 c) LNA3 d) LNA4

Table 1- Executive Characteristics Designed LNAs

| $S_{11}$ | < -10 dB |

|----------|----------|

| $S_{22}$ | <-10 dB  |

| $S_{21}$ | > 10 dB  |

| NF       | < 4 dB   |

| IIP3     | > -1 dBm |

| $P_{DC}$ | < 1 mW   |

| $f_C$    | 2.4 GHz  |

band of Medical Science Industrial (ISM). As can be seen in Table 1, the required

The working frequency of the low-noise amplifier signal should be in the 2.4 GHz

gain and linearity cannot be freely optimized for this reason.

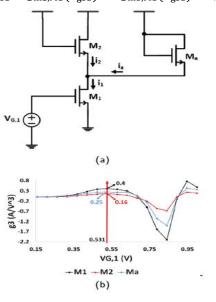

In Figure 2(a), the transient $M_1$  is the main  $istori_2$  and the connected diode also states the power as (1)

$$i_2 = i_1 - i_a$$

(1)

original source $M_1M_2M_q$  of The  $i_1 i_2 i_a$ derived from third-order IMD3 is nonlinearity,  $M_1$  because the generated nonlinear current is fully transmitted, acting as a flow  $M_1M_2$  buffer. If the discharge  $has M_1 an$  additional flow path selectively cancels the IMD3 flow component, then a flow component The IMD3 is  $M_2$  smaller to be transmitted. Thus, the  $M_a$  transistor connected to the diode, which acts as IMD3, is added to the LNA1 as Figure 2(a).

LNA characteristics are determined as an increase in voltage of at least 10 dB and a noise value of less than 4 dB. The input and output reflection coefficients should be less than -10 dB. A low-noise amplifier with less than 1 mW total power Consumes while having IIP3 higher than -1 meters. Although the performance specification listed for an LNA with a narrow band is relatively modest, it should be emphasized that the purpose of these criteria is to yield less than 1 mW of power consumption. In this respect, similar to a case of large-band LNA operation, the coefficient cannot be Reduce noise as much as it should because the current required for that performance exceeds the limit imposed by power consumption. Moreover, voltage

The n-MOSFET drain current can be supplied using the power series expansion as follows:

$$i_d = g_{m1} + g_{m2}(V_{gs})^2 + g_{m3}(V_{gs})^3$$

(2)

$i_{\rm d}=g_{\rm m1}+g_{\rm m2}\big(V_{\rm gs}\big)^2+g_{\rm m3}\big(V_{\rm gs}\big)^3\quad (2)$  where the  $g_{mi}$  transition is nth. And also,  $i_1$ , in the form of and the power  $i_a$

$$i_1 = g_{m1,M1}V_{gs1} + g_{m2,M1}(V_{gs1})^2 + g_{m3,M1}(V_{gs1})^3$$

(3)

Figure 2- a) LNA With a NMOS Deadly IMD bthe Third Order Transitional Guidance M1,M2,Ma

$$i_{a} = g_{m1,Ma} V_{gsa} + g_{m2,Ma} \big( V_{gsa} \big)^{2} + g_{m3,Ma} \big( V_{gsa} \big)^{3} \quad (4)$$

ignored. Therefore, the number  $i_a$  of terms  $V_{gs1}$  can be found:

$$i_{a} = g_{ma,Ma}c_{1}V_{gs1} + g_{m2,Ma}c_{2}(V_{gs1})^{2} + g_{m3,Ma}c_{3}(V_{gs1})^{3}$$

(6)

Considering (2)–(6) to (1), it will be equal to: $i_2$

Where and  $soV_{gs1}V_{gsa}$  on stands for gatesource  $M_1$  voltage. The function  $M_aV_{qsa}$  of the is, therefore  $V_{gs1}$ , can be  $V_{gsa}$  extended using the power series,

$$V_{gsa} = c_1 V_{gs1} + c_2 (V_{gs1})^2 + c_3 (V_{gs1})^3$$

(5)

Where  $c_i$  the coefficient is dependent on frequency. A first-order approximation is sufficient to prove the cancellation, so the second- and third-order components are

531 mVHowever, the voltage increase is also due to a decrease in the expression () of the eternal decrease  $g_{m1,M1} - c_1 g_{m1,Ma}$ . Therefore, as shown in Figure 1(d), add to the voltage gain to increase the voltage gain $M_h$ .

The LNA4 is designed with a high linearity in Figure  $1(\mathrm{d}L_g)$ , which includes over-the-chip and off-chip versions. The off-chip goal is to obtain  $L_g$ a high-quality factor and thus reduce the occupied chip

$g_m$  In LNA without the technique of improving voltage gain is equal to transmitting conductivity, while in  $g_{m1,M1} = 11.24 \, mSLNAg_m$  with the technique of improving the voltage increase, the sum and,  $g_{m,M1}$ hereby, bringing the total to 13.31  $g_{m,Mb}$ mS. Iodine $M_b$  measurements are made so that the current balance of IMD is not disrupted to maintain linear operation.

$$\begin{split} i_2 &= \left(g_{m1,M1} - c_1 g_{1,Ma}\right) V_{gs1} \\ &+ \left(g_{m2,M1} \\ &- c_1^2 g_{m2,Ma}\right) \left(V_{gs1}\right)^2 \\ &+ \left(g_{m3,M1} \\ &- c_1^3 g_{3,Ma}\right) \left(V_{gs1}\right)^3 \end{split} \tag{7}$$

The coefficients, and depend on the frequency  $c_1c_2c_3$ , and have  $c_1$  a positive sign because 1 draws the current proportionally ( $M_a$  Kim and Kim, 2006). In addition, it aims to cancel the byas-gate mode. However, IMD3 is  $(g_{m3,M1}-c_1^3g_{m3,Ma})$  not completely cancelled due to the limited amount of power allocated, so the circuit is designed to minimize the IMD3 component .

In Figure 2(b), the third-order () transconductance diagrams for the  $g_{m3}s$ , and by taking the derivative of the third order Jerian $M_1$  the  $M_2M_a$  discharge of the corresponding transistor were obtained according to the following. The value ranges from 400 mA/V3  $V_{gs1}g_{m2,M2}$  to 160 mA/V3 and P=986.6 $\mu$ W.  $V_{gs1}$

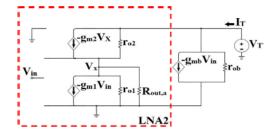

Figure 3- Small signal equivalent Suggested LNAs

Figure 4- Display values Towards And the doctors. Designed LNAs

${\rm LNA1}^1/g_{ma} \ll r_{o1}, r_{oa}.$  When  $M_b$  represented, due to the maximum power requirement of 1 mW, the operating current of the cascaded stage decreases slightly. Reducing cascad stage flow increases  $R_{OUT}$  even if it is  ${\rm in} r_{ob}$  the shunt with cascad exit resistance . Also, AZ,  $g_m M_b$  amplifies

The output resistance of LNA2, by adding an eternal  $\mathrm{dm}R_{OUT}M_a$ . In Figure  $3R_{OUT,a}$ , it is equal to, while  $^1/g_{ma}$ )|| $r_{oa}R_{OUT}$  for LNA1, it is  $g_{m2}r_{o2}r_{o1}$  in LNA2 $g_{m2}r_{o2}\left(r_{o1}\left|\left|\frac{1}{g_{ma}}\right|\right|r_{oa}\right)$ .  $R_{OUT}$ LNA2 is smaller than

GHz, respectively. Therefore, it  $M_b$  does not reduce LNA stability.

## 3. Simulation Results and Discussion

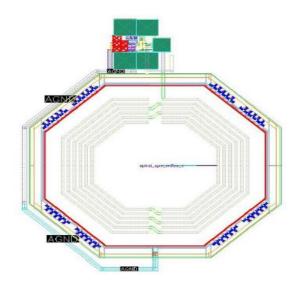

The proposed high-linearity LNA is designed in a 40nm commercial CMOS process technology with a supply voltage.  $V_{DD} = 1 V$  Current consumption is 989.6 μA. All LNAs are built and optimized to operate at a frequency of 2.4 GHz. Simulations were performed in Cadence Virtuoso and R+C+CC was selected as the extraction type, which included all the jamming resistances, The jamming capacitors and coupling capacitors are in post-layout simulations. Table 2 presents channel geometry (µm|nm) of transistors and values of components. Channel B length is  $M_2$  chosen more than other transistors for larger cascad output resistance. Quality factors are both and  $L_a$ 80  $L_b$  which are determined as off-chip inductors. Also the inductor quality factor on the chip  $L_d$  is 7.12 evaluated. Figure 5 shows the final layout of the LNA plan, which occupies an area of 0.085 mm<sup>2</sup>.

LNA, because a Provides voltage gain path in shunt with cascaded amplifier. Increases both and increases  $R_{OUT}g_m$  the LNA3 voltage .

A spiral inductor has not been used in the source because the bonded wires previously produced an induction effect there. Typically, band wires have a higher quality factor than spiral inductors, which helps to reduce noise resistance and help with noise. By removing spiral inductors, the total surface area of the chip is also reduced. The inductance value of the bonded wire here is 500 pH It has been selected that may be achieved using two parallel link wires each having a typical inductance of 1 nH.  $M_b$  Directly connected to the input. Hence, stability must be checked. Unconditional stability conditions are shown in terms of S parameters in (8) and (9) [7].

$$K = \frac{|\Delta| = |S_{11}S_{22} - S_{12}S_{21}| < 1 \quad (8)}{1 - |S_{11}|^2 - |S_{22}|^2 + |S_{11}S_{22} - S_{12}S_{21}|^2}{2|S_{12}S_{21}|} > 1 \quad (9)$$

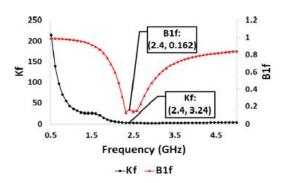

In Figure 4, and  $K_f$ B1f, which refer to K and  $|\Delta|$ , are equal to 3.24 and 0.162 at 2.4

Table 7- Elements and transistor size ratiosW/L

| $M_1$   | 32 µm   40 nm  | $C_1$    | 200 pF |

|---------|----------------|----------|--------|

| $M_2$   | 16 μm   150 nm | $L_b$    | 750 pH |

| $M_a$   | 8 μm   40 nm   | $C_{ex}$ | 712 fF |

| $M_b$   | 44 μm   40 nm  | $L_d$    | 8.5 nH |

| $L_{g}$ | 2.2 nH         | $C_2$    | 483 fF |

|         |                |          |        |

Figure 5- Layout Related to LNA4 Designed

output impedances (respectively db and  $S_{11} = -27$  des-bell). In Figure  $6(aS_{22} = -17)$ , it is shown that the

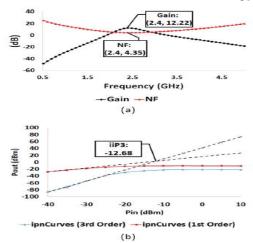

Figure 6(a) and 6(b) shows the performance of LNA1 when set to operate at 2.4 GHz. It has matching input and

signal. The gate bias and size are set  $for M_a deletion g_{3,M2}$ . Due to the power consumption limit, it cannot be completely removed. However,  $g_{3,M2}$  it can be reduced to a sufficient amount of IIP3 to increase the IIP3 value by approximately 12.5 dB/m. In Figure  $\Lambda(a)$  and  $\Lambda(b)$ , the performance of LNA<sup>\gamma</sup> is illustrated by linear improvements and voltage gains. This shows that the voltage gain increases by approximately 6 dB without reducing the performance of )IIPT. Figure Aa shows that the voltage ( gain andNF have improved to 11.1 and 4.27 dB, respectively. In Figure 8 (b), IIP<sup>7</sup> It is  $\cdot/\Lambda \Upsilon$ -dBm. It is also the values  $S_{11}$  and  $S_{22}$  less than - \ \ dB. Finally, it is stored in the LNA $L_q$  on the chip.

designed LNA1 achieves an increase of 12.22 dB. The noise factor is also 4.35 dB. Finally, Figure 6 ( (b) An IIP3 is equal to 12.68 dBm.

Figure 7(a) and 7(b) shows LNA2 performance with improved linearity at 2.4 GHz. Input and output reflection coefficients meet design specifications (dB and dB, respectively). In Figure 7 (a), the voltage gain decreases from 12.2 dB to 5.68 dB, while IIP3 is reduced from 12.68 dB to 0.12  $S_{11} = -17.97S_{22} = -23$  dB in Figure 7 (b) increased. In addition, NF increased to 5.13 dB.

In Figure 2(b), $M_a$  IIP3 is added to the LNA1. It is also $M_a$  used to reduce IMD3  $M_2$  with injectable flow. It decreases with the refining  $g_{3,M2}g_{3,Ma}g_{3,M1}$  of the same

Figure - 7 a Gain Voltage and NF b (IIP3 Related to LNA1

Figure 7- aGain Voltage and NF b) IIP3 Related to LNA2 With improved line

Figure  $^{r_i}$  the voltage gain is added to the LNA2 .to increase the voltage gain However the voltage  $M_b$  between the input and output ports of the LNA reduces

While IIP3 decreases by improving  $g_{3,M2}$  the indefinitely the voltage gain through the loss in as shown in  $({}^{\lor})g_{m,M2}$  decreases the  $M_b$  indefinitely. As shown in

critical in LNA performance in the layout. Therefore, these paths are drawn along with the input and output paths to reduce the wider jamming resistance . Therefore, there is no significant change in and  $S_{11}$ It  $S_{22}$  is not seen in post-installation simulations.

As seen in Figure 11(a), the LNA designed in post-layout simulations achieves a voltage gain of 10.31 dB. The loss of gain in postlayout simulation results is due to the jamming resistance. Figure 11(b) shows that NF increases with decreasing voltage gain.

,Finally IIP3 was enhanced in post-layout ,simulations compared to pre-layout results as shown in the figures . Figure \(^{\gamma}(a)\) and \(^{\gamma}(b)\). The induction effect between the source and the ground causes a linear increase and a decrease in gain. The increase in linear results of post-layout simulations arises from source .degeneration due to noise resistances

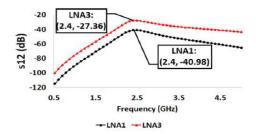

the cascade which is determined by the parameter.  $S_{12}$  is Therefore Iodine  $M_b$  measured in such a way that it increases the gain of the voltage without being dominant enough to reduce the separation. This has been investigated in Figure  $^{9}$  and it is observed that the  $^{17}$  dB  $S_{12}$  has increased but this change in design specifications is , .considered tolerable

Figures 10, 11 and 12 show the functions before and after the LNA layout  $L_g$  by improving the linearity and increasing voltage (off the chip). According to Figure 10(a) and 10(b), input and output reflection coefficients at 2.4GHz are acceptable, with  $S_{11} = -19.36$  (pre-set) and desibel (after layout) () decibel  $S_{11} = -13.35$  (pre-installation) and  $S_{22} = -21.21$  desibel  $S_{22} = -15.42$  (after layout). The  $S_{22}$  is important because the designed LNA is modular. Hence, it can be applied to different receiver structures. DC lines that pass through the incoming RF path are

Figure - A a Gain Voltage and NF b (IIP3 Related to LNA3With linear and improved voltage gain

Figure 9- S12 Related to LNA1 and LNA3

table 3-Run LNA4 In different processes and temperatures

| Temperature          | SS    |       |       | FF    |       |       | FS    |       |       | SF    |       |       |

|----------------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

|                      | 0 °C  | 25 °C | 75 °C | 0 °C  | 25 °C | 75 °C | 0 °C  | 25 °C | 75 °C | 0 °C  | 25 °C | 75 °C |

| S <sub>11</sub> (dB) | -9    | -9    | -9    | -8.75 | -9.33 | -10.6 | -12   | -13.0 | -14.6 | -12.7 | -13.6 | -15.4 |

| $S_{22}$ (dB)        | -22.6 | -21.1 | -19   | -13.4 | -12.9 | -12.3 | -15.6 | -15.0 | -14   | -16.9 | -16.5 | -15.8 |

| $S_{21}$ (dB)        | 7     | 6.57  | 5.65  | 13.5  | 13.22 | 12.7  | 11    | 10.64 | 9.88  | 10.4  | 9.99  | 9.2   |

| NF (dB)              | 4.5   | 4.99  | 5.97  | 2.36  | 264   | 3.2   | 3.22  | 3.6   | 4.35  | 3.33  | 3.72  | 4.5   |

| IIP3 (dBm)           | 7.73  | 8.18  | 7     | -2.56 | -2.69 | -2.43 | -0.20 | -0.32 | -0.07 | 4.38  | 3.69  | 3.74  |

Figure - \ a (S11 b( S22 Related to LNA4With improved line and voltage gain

Figure 11- aGain Voltage b) NF Related to LNA4 With improved line and voltage gain

temperature decreases, the voltage rise increases whileNF decreases. Degraded SS for S<sub>11</sub> and FF process corners. Other than that, other performance parameters are acceptable

The performance parameters of LNA4 are simulated in four different process corners (SS ,FF, FS, and SF) and three different temperatures (0°C, 25°C and 75°C). The results are presented in Table 3. As the

Figure - \ TIP3 a ( Pre-Layoutb ( Post-LayoutLNA4With linear and improved voltage gain

table 4-Analysis MC Related to LNA4

|                      | Best value | Worst value | Mean   |

|----------------------|------------|-------------|--------|

| S <sub>11</sub> (dB) | -27.2      | -8.53       | -14.01 |

| $S_{22}$ (dB)        | -24.52     | -12.09      | -16.91 |

| $S_{21}$ (dB)        | 12.19      | 7.99        | 10.24  |

| NF (dB)              | 2.95       | 4.66        | 3.73   |

| IIP3 (dBm)           | 9.44       | -5.27       | 2.2    |

table 4-RunSuggested LNAs

|                     | LNA1   | LNA2   | LNA3   | LNA4 (pre-layout) | LNA4 (post-layout) |

|---------------------|--------|--------|--------|-------------------|--------------------|

| $S_{21}$ (dB)       | 12,22  | 5.68   | 11.1   | 11.49             | 10.31              |

| NF (dB)             | 4.35   | 5.13   | 4.27   | 3.38              | 3.68               |

| $S_{11}$ (dB)       | -27    | -17.97 | -21    | -19.36            | -13.35             |

| $S_{22}$ (dB)       | -16    | -23    | -14.78 | -21.21            | -15.42             |

| IIP3 (dBm)          | -12.68 | -0.12  | -0.82  | -0.7              | 0.89               |

| P1dB (dBm)          | -23.74 | -12.13 | -13.57 | -11.54            | -11.16             |

| $P_{DC}$ ( $\mu$ W) | 995.6  | 986.6  | 997.2  | 1079              | 989.6              |

| FOM                 | 0.198  | 1.36   | 2.82   | 6.10              | 7.05               |

|                     |        |        |        |                   |                    |

Figure 13Differences in the histogram parameters in Monte Carlo simulation. a) S11 b) S22 C) S21 D) NF e) IIP3

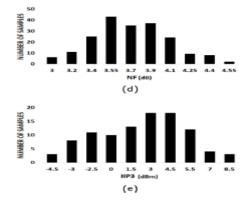

IIP3) in Figure 13. Table 4 lists the worst, best, and average values of performance parameters obtained in the MC simulation.

The performance of LNA4 is also examined under process changes and mismatches using Monte Carlo analysis (MC) of more than 200 samples (100 for

table 6- Compare the proposal with others LNAha

|                         | Gain (dB)   | NF (dB)  | IIP3 (dBm)         | $P_{dc}$ ( $\mu$ W) | $F_c$ (GHz)    | Tech. (nm) | FOM  |

|-------------------------|-------------|----------|--------------------|---------------------|----------------|------------|------|

| This Work (post-layout) | 10.31       | 3.68     | 0.89               | 989.6               | 2.4            | 40         | 7.05 |

| [12] (measurement)      | 11          | 6.8      | -2.2               | 174                 | 2.4            | 65         | 6.56 |

| [13] (post-layout)      | 18.2        | 3.38     | -4.32              | 967                 | 2.4            | 180        | 2.93 |

| [14] (post-layout)      | 14          | 3.45     | -8                 | 980                 | 2.4            | 180        | 0.92 |

| [8] (pre-layout)        | 14          | 5.2      | -8.6               | 30                  | 2.4            | 40         | 15.2 |

| [15] (measurement)      | 12.6        | 5.5 ~6.5 | -9                 | 750                 | 0.1~7          | 90         | 0.47 |

| [16] (measurement)      | 12.3        | 4.9~16   | -9.5               | 400                 | $0.1 \sim 2.2$ | 130        | 0.87 |

| [17] (measurement)      | 14          | 4~6      | -10                | 250                 | 0.6~4.2        | 130        | 1.87 |

| [18] (measurement)      | 17.4        | 2.8      | -10.7              | 480                 | 2.4            | 65         | 1.71 |

| [9] (measurement)       | 13.9        | 8.9      | -13                | 69                  | 2.4            | 65         | 1.27 |

| [19] (measurement)      | 12,2        | 1.9~2.2  | -16                | 350                 | 3~5            | 130        | 0.97 |

| [10] (measurement)      | 21.5        | 6.3      | -16                | 900                 | 2.4            | 28         | 0.11 |

| [11] (measurement)      | 6.9         | 3        | -18                | 44                  | 2.4            | 16         | 1.25 |

| [20] (post-layout)      | 13.64~15.64 | 4.5~6    | <del>-</del> 5~ -6 | 600                 | 0.03~3         | 180        | 1.30 |

| [21] (measurement)      | 16.8        | 6.6      | -16.4              | 350                 | 4              | 28         | 0.20 |

In Table 6, the performance criteria of LNA4 are compared with the different results of low-power LNAs reported in the paper with working frequency in the range of 0.1 GHz to 7 GHz. Although the FOM [8] is higher than that of LNA4, its IIP3 is roughly equal to LNA1. Except [8], LNA4 in terms of value FOM is the best among all comparable studies. In addition, power consumption [9] is substantially low. However, its NF is very high, and the amount of IIP3 reported is much lower than the LNA4 design described in this work. Also, [10] and [11] are notable in terms of the use of CMOS technologies at the deep nanoscale. However, NF [10] is very high, while voltage gainers [11] are significantly low.

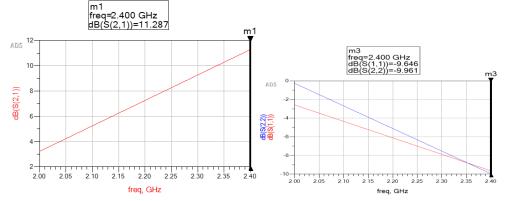

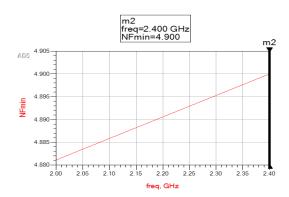

## 4. Comparison of simulation

The results of theory and simulation have been achieved by  $^{\circ}$  nm  $S_{21}=12-19$  dB .process but in the process of  $^{\circ}$  nm dB Similarly, other parameters are decibel and dB, but in other processes for  $M_3$   $S_{21}=11.287S_{11}=-27.2S_{22}=-24.52S_{11}=-9.646S_{22}=-9.961$  dB and also noise coefficient is  $^{\circ}$ / $^{\circ}$  dB in  $^{\circ}$  nm process and

Table 5 summarizes the performance of four different LNAs. While LNA1 is not suitable for satisfying linear specifications, the performance of IIP3 has improved dramatically by approximately 12.5 mB in LNA2, thus meeting the requirements. However, the voltage gain and NF LNA2 are much lower than the specifications. Although the voltage gain performance of IIP3 in LNA3 Enhanced, this topology may occupy a large chip area due to the input matching circuit on the chip. By removing the outside of the chip, all  $L_a$ LNA4 performance subordinates conform to the basic design specifications. Since it is  $L_q$  off-chip, it can be considered a high quality factor that further improves overall performance. When the number of competencies (FOM) calculated based on the expression presented in (10), compared out of the four LNA topologies, LNA4 is the most successful of all in terms of performance metrics achieved.

$$= \frac{\text{Gain (dB)} \times \text{IIP3 (}\mu\text{W}\text{)}}{(\text{NF (dB)} - 1 \times \text{Power (}\mu\text{W}\text{)}} \quad (10)$$

and 19, and the summary of the 14,14 results is also shown in the table

in Fb nm process equal to 4.9 dB is obtained. The results are shown in Figures

Figure - 14 S21 Related to LNA445nm

Figure 15-S11 and S22 Related to LNA4 45nm

Figure 16- NF Related to LNA4 45nm

.table \(^{\text{A}}\) summary of the results of the simulation

| $V_{DD}$ | $I_{DD}$ | Power | Technology | S <sub>21</sub> | BW      | Noise |

|----------|----------|-------|------------|-----------------|---------|-------|

| 1v       | 815uA    | 815uW | Cmos 45nm  | 11.2dB          | 2400MHz | 4.9dB |

# 5. Conclusion

In this paper, four LNAs are designed using two different techniques to improve linearity and gain voltage in power below mW in a 40-nm CMOS commercial process at 2.4 GHz. The proposed LNA, LNA4, with a 1 volt power supply, achieves an IIP3 digit of 0.89 dBm and wastes 989.6 microwatts at 2.4 GHz. It has a voltage gain of 10.31 dB and a noise coefficient of 3.68 dB. Based on its design criteria, LNA4 can be used in very low-power and high-performance receivers, as it is often encountered in biomedical applications.

# **Refereces:**

- C.-T. Hsiao, Design of a 2.4 GHz CMOS LNA For Bluetooth Low Energy Application Using 45 nm Technology (Master's thesis), San Jose State University, 2017, Available at <a href="https://scholarworks.sjsu.edu/cgi/viewcontent.cgi?article=8349&context=etd">https://scholarworks.sjsu.edu/cgi/viewcontent.cgi?article=8349&context=etd</a> theses.

- H.-J. Liu, Z.-F. Zhang, An ultra-low power CMOS LNA for WPAN applications, IEEE Microw. Wirel. Compon. Lett. 27 (2) (2017) 174–176.

- 3. A. Nadia, H. Belgacem, F. Aymen, A low power low noise CMOS amplifier for bluetooth applications, in: 2013 International

- Conference on Applied Electronics, IEEE, 2013, pp. 1–4.

- 4. M.B. Yelten, K.G. Gard, A novel design procedure for tunable low noise amplifiers, in: 2009 IEEE 10th Annual Wireless and Microwave Technology Conference, IEEE, 2009, pp. 15,http://dx.doi.org/10.1109/WAMICON.200 9.5207313.

- A. Çağlar, M.B. Yelten, Design of cryogenic LNAs for high linearity in space applications, IEEE Trans. Circuits Syst. I. Regul. Pap. 66 (12) (2019) 4619–4627, <a href="http://dx.doi.org/10.1109/TCSI.2019.2936506">http://dx.doi.org/10.1109/TCSI.2019.2936506</a>

- 6. T.-S. Kim, B.-S. Kim, Post-linearization of cascode CMOS low noise amplifier using folded PMOS IMD sinker, IEEE Microw. Wirel. Compon. Lett. 16 (4) (2006) 182–184.

- 7. G. Gonzalez, Analysis and design, Microw. Transistor Amplif. (1997).

- E. Kargaran, D. Manstretta, R. Castello, Design and analysis of 2.4 GHz 30 μw CMOS LNAs for wearable wsn applications, IEEE Trans. Circuits Syst. I. Regul. Pap. 65 (3) (2017) 891–903.

- A. Dissanayake, H.-G. Seok, O.-Y. Jung, S.-K. Han, S.-G. Lee, A 64 μw, 23 dB gain, 8 dB NF, 2.4 GHz RF front-end for ultra-low power internet-of things transceivers, in: 2017 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), IEEE, 2017, pp. 184– 187.

- J. Zaini, F. Hameau, T. Taris, D. Morche, P. Audebert, E. Mercier, A tunable ultra low power inductorless low noise amplifier exploiting body biasing of 28 nm FDSOI technology, in: 2017 IEEE/ACM International Symposium on Low Power Electronics and Design (ISLPED), IEEE, 2017, pp. 1–6.

- 11. Y.-T. Lu, J.-D. Jin, 100-MV 44-μw 2.4-GHz LNA in 16 nm FinFET technology, in: 2016 IEEE MTT-S International Microwave Symposium (IMS), IEEE, 2016, pp. 1–3.

- 12. K. Xu, J. Yin, P.-I. Mak, R.B. Staszewski, R.P. Martins, A single-pin antenna interface RF front end using a single-MOS DCO-PA and a push-pull LNA, IEEE J. Solid-State Circuits 55 (8) (2020) 2055–2068.

- 13. A. Karimlou, R. Jafarnejad, J. Sobhi, An inductor-less sub-mw low noise amplifier for wireless sensor network applications, Integration 52 (2016) 316–322.

- F. Rastegari, M. Dousti, B. Ghalamkari, A 0.75 V sub-mW CMOS LNA employing

- transmitted signal suppression technique in a full-duplex wireless brain machine interface transceiver, AEU-Int. J. Electron. Commun. 132 (2021) 153632.

- 15. M. Parvizi, K. Allidina, M.N. El-Gamal, A sub-mw, ultra-low-voltage, wideband low-noise amplifier design technique, IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 23 (6) (2014) 1111–1122

- M. Parvizi, K. Allidina, M.N. El-Gamal, An ultra-low-power wideband inductorless CMOS LNA with tunable active shunt-feedback, IEEE Trans. Microw. Theory Tech. 64 (6) (2016) 1843–1853.2.

- M. Parvizi, K. Allidina, M.N. El-Gamal, Short channel output conductance enhancement through forward body biasing to realize a 0.5 V 250 μw 0.6 4.2 GHz current-reuse CMOS LNA, IEEE J. Solid-State Circuits 51 (3) (2015)574–586.

- M. Rahman, R. Harjani, A 2.4-GHz, sub-1-V, 2.8-dB NF, 475-μw dual-path noise and nonlinearity cancelling LNA for ultra-low-power radios, IEEE J. Solid-State Circuits 53 (5) (2018) 1423–1430.

- A.M. Saied, M.M. Abutaleb, M.I. Eladawy, H. Ragai, Ultra-low power LNA design technique for UWB applications, AEU-Int. J. Electron. Commun. 97 (2018)149–153.

- A.P. Tarighat, Ultra-low power inductorless differential LNA for WSN application, Analog Integr. Circuits Signal Process. 108 (2) (2021) 409–419.

- 21. T. Taris, J. Desevedavy, F. Hameau, P. Audebert, D. Morche, Inductorless multimode RF-CMOS low noise amplifier dedicated to ultra low power applications, IEEE Access 9 (2021) 83431–83440.